- Die & Wafer

- +Supplier Line Card

- Alliance Memory

- Analog Devices

- Apogee Semiconductor

- Analog Power

- Avalanche Technology

- Central Semiconductor

- Diodes Incorporated

- Cypress

- Everspin Technologies

- Interfet

- International Rectifier

- ISOCOM Limited

- ISSI

- Knowles

- Linear Integrated Systems

- MACOM Technology

- Microchip

- Micron Technology

- NXP Semiconductors

- On Semi

- Renesas

- Samsung Semiconductors

- SemiQ Inc.

- Semicoa

- Texas Instruments

- Transys

- Vishay

- VPT Components

- +Quick Turn Services

- +Wafer Processing

- +EOL/DMSMS Sustainment

- +Component Design & Packaging

- Advanced Interconnect Technologies

- 2.5 & 3D Heterogeneous Integration

- System in Package (SiP)

- Multi-Chip Modules (MCMs)

- Wafer Bumping & WLP

- Design, Packaging & Assembly

- Assembly Services

- Chip on Board (CoB)

- Plastic Packaging (BGA/CSP/QFN)

- Hermetic Packaging

- OSAT Services

- +Supplier Line Card

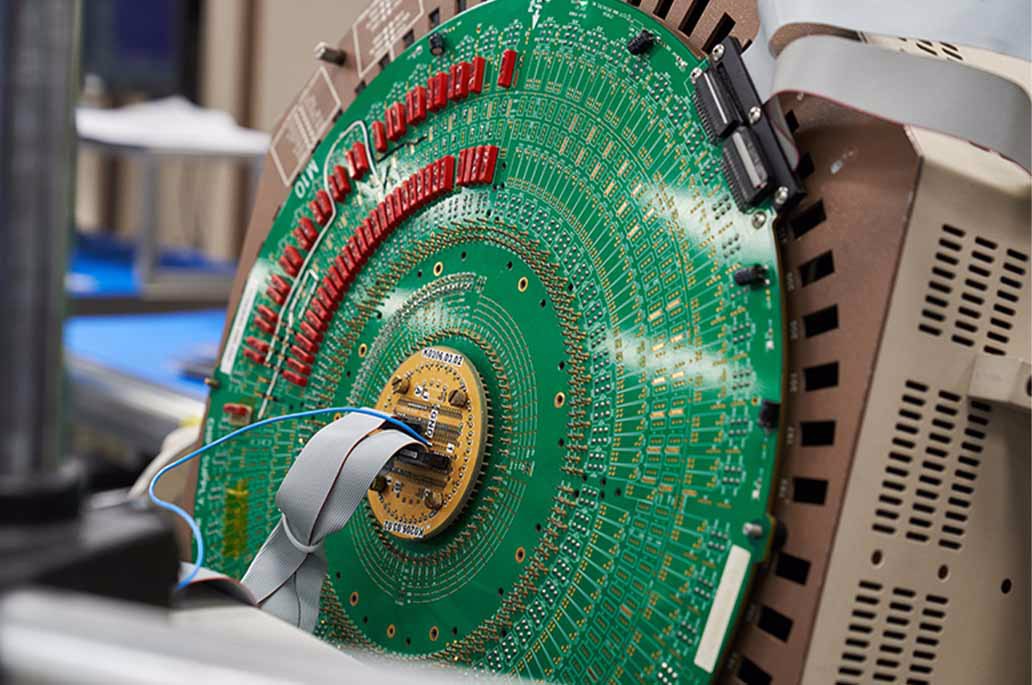

The industry standard regarding test for part number sold as bare die and wafer is that all devices are 100% probed at 25 degrees C for DCs and functionals. For customers using die in a hybrid circuit a lot acceptance test or element evaluation may be required. This testing is performed on a sample of die from one lot that is packaged and electrically tested per the device data sheet or per the customer's drawing. Lot testing is done to verify the element characteristics required and to assure device performance meets the specified conditions as experienced in the application.

Our Capabilities

- Selected Parameter Probe

- Hot & Cold Chuck Temperature Probing

- Lot Acceptance Testing (LAT)

- Up to 12" Wafer Capacity, Final Test at Wafer Level

- Conversion Between Industry Formats

- Inking Using Any Electronic Wafer Map